반응형

1. 시스템의 구성

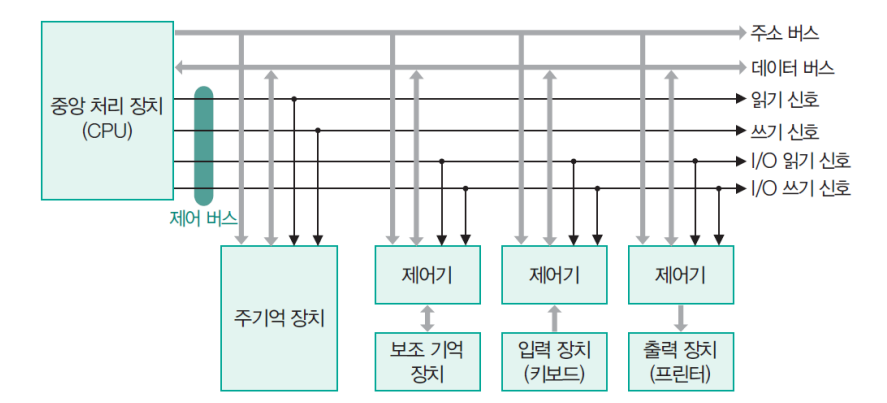

CPU와 시스템 버스 간의 접속

시스템버스

- CPU와 기억 장치 및 입출력 장치 사이에 정보를 교환하는 통로

- 기본구성

- 주소 버스(address bus)

- 데이터 버스(data bus)

- 제어 버스(control bus)

주소 버스(address bus)

- CPU가 기억 장치나 입출력장치를 지정하는 주소 정보를 전송하는 신호선들의 집합

- 단방향(uni-directional)전송 : 주소는 CPU로부터 기억장치 혹은 I/O 장치로 보내지는 정보

- 주소선의 수는 CPU와 접속될 수 있는 최대 기억장치 용량을 결정

- [예] 주소 버스의 비트수 = 12 비트라면, 최대 212= 4K 개의 기억 장소들의 주소를 지정 가능

데이터 버스(Data bus)

- CPU가 기억 장치나 입출력 장치 사이에 데이터를 전송하기 위한 신호선들의 집합

- 양방향(bi-directional)전송 : 읽기와 쓰기 동작을 모두 지원

- 데이터선의 수는 CPU가 한 번에 전송할 수 있는 데이터 비트의 수를 결정

- [예] 데이터 버스 폭 = 32 비트라면 CPU와 기억장치 간의 데이터 전송은 한 번에 32비트씩 가능

제어 버스(Control bus)

- CPU가 시스템 내의 기억장치 및 I/O등 각종 요소의 동작을 제어하는데 필요한 신호선들의 집합

- 기억장치 읽기 / 쓰기(Memory Read / Write) 신호

- I/O 읽기 / 쓰기 (I/O Read / Write) 신호

- 인터럽트(Interrupt) 신호

- 버스 제어(Bus Control) 신호

- 설계는 양방향이지만, 주로 단방향 사용

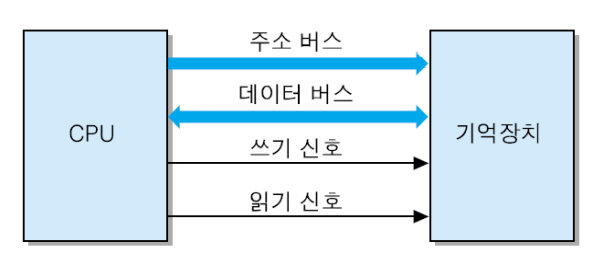

CPU와 기억장치의 접속

엑세스(access)

- CPU가 데이터를 기억장치의 특정 장소에 쓰거나(저장) 이미 저장된 내용을 읽는 동작

기억장치 액세스에 필요한 버스 및 제어신호

- 주소 버스

- 데이터 버스

- 제어 신호 : 기억장치 읽기(memory read) 신호, 기억장치 쓰기(memory write) 신호

CPU와 기억장치 간의 접속

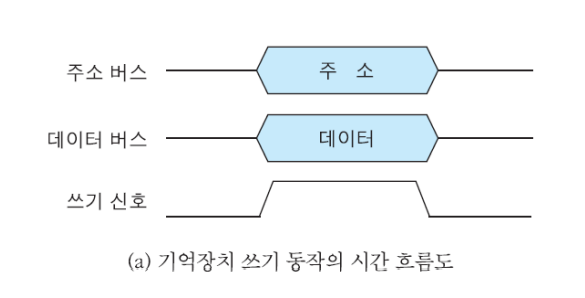

기억장치 쓰기 동작

- CPU가 데이터를 저장할 기억장소의 주소와 저장할 데이터를 각각 주소 버스와 데이터 버스를 통하여 보내는 동시에, 쓰기 신호를 활성화(activate)

- 기억장치 쓰기 시간(memory write time) : CPU가 주소와 데이터를 보낸 순간부터 저장이 완료될 때까지의 시간

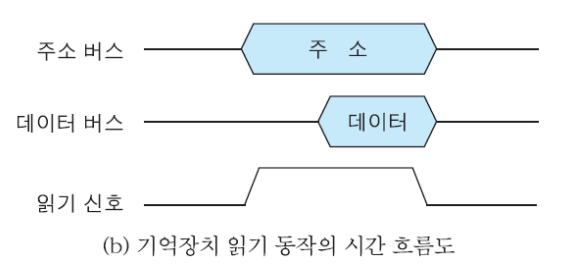

기억장치 읽기 동작

- CPU가 기억장치 주소를 주소 버스를 통하여 보내는 동시에, 읽기 신호를 활성화

- 일정 지연 시간이 경과한 후에 기억장치로부터 읽혀진 데잍가 데이터 버스상에 실리고, CPU는 그 데이터를 버스 인터페이스 회로를 통하여 읽음

- 기억장치 읽기 시간(memory read time) : 주소를 발생한 시간부터 기억장치의 데이터가 CPU에 도착할 때까지의 시간

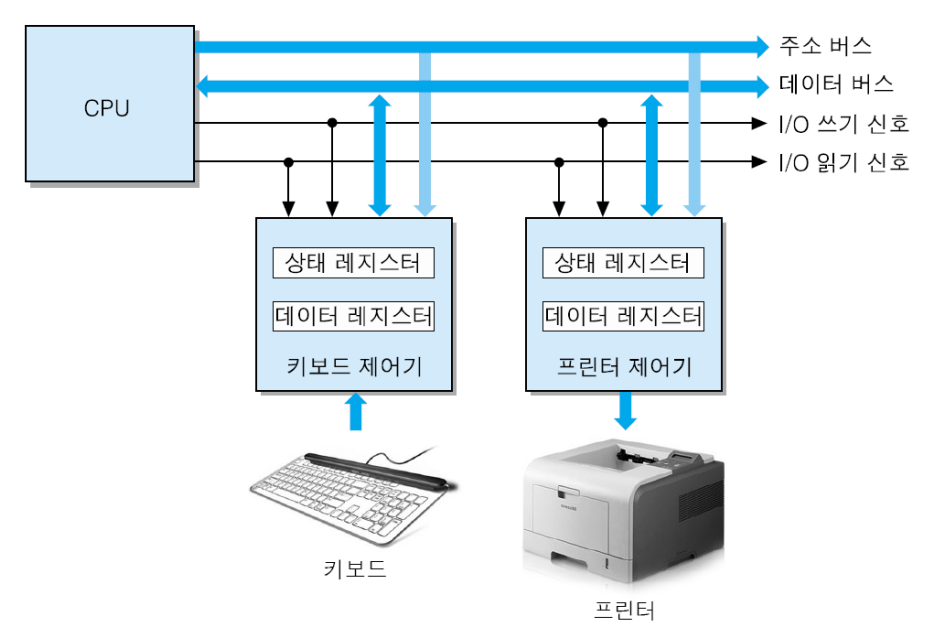

CPU와 I/O 장치의 접속

필요한 버스 및 제어 신호

- 주소 버스

- 데이터 버스

- 제어 신호 : I/O 읽기 신호, I/O 쓰기 신호

접속 경로

- CPU <-> 시스템 버스 <-> I/O장치 제어기 <-> I/O 장치

I/O 장치 접속 사례 : CPU - 키보드 & 프린터

I/O 장치 제어기(I/O device controller)

I/O 장치 제어기

- CPU로 부터 I/O 명령을 받아서, 해당 I/O장치를 제어하고, 데이터를 이동함으로써 명령을 수행하는 전자회로 장치

- 키도브 제어기, 프린터 제어기 등

상태 레지스터

- I/O 장치의 현재 상태를 나타내는 비트들을 저장한 레지스터

- 준비 상태(In_RDY) 비트, 데이터 전송 확인(acknowledgment, ACK) 비트 등

데이터 레지스터(데이터 버퍼)

- CPU와 I/O 장치 간에 이동되는 데이터를 일시적으로 저장하는 레지스터

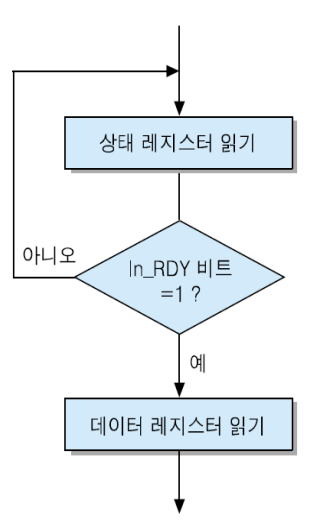

키보드의 데이터 입력 과정

키보드 제어기

- 키보드의 어떤 한 키(key)를 누르면, 그 키에 대응되는 ASCII코드가 키보드 제어기의 데이터 레지스터에 저장

- 동시에 상태 레지스터의 In_RDY 비트가 1로 세트

CPU

- ①키보드 제어기로부터 상태 레지스터의 내용을 읽어서 In_RDY 비트가 1로 세트 되었는지 검사

- In_RDY 비트는 데이터 레지스터에 외부로부터 데이터가 적재 되었는지를 표시

- 만약 세트 되었다면, 데이터 레지스터의 내용을 읽음

- 만약 세트 되지 않았으면, ① 반복하며 대기

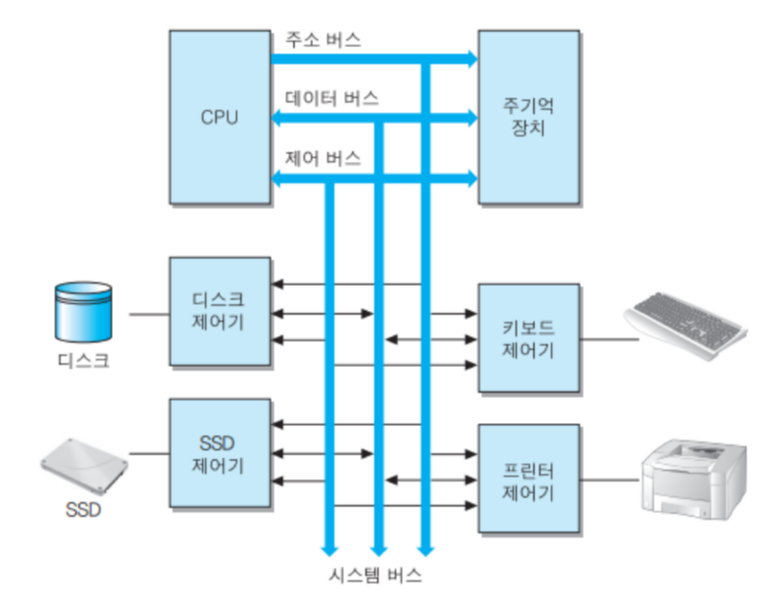

CPU와 보조 기억장치의 접속

- 보조 기억장치들(하드 디스크, SSD, 플래시 메모리 등)도 각 장치를 위한 제어기를 통하여 키보드나 프린터와 유사한 방법으로 접속

- CPU는 보조 기억장치의 제어기를 통해서 접속

차이점 : 데이터 전송 단위

- 키보드 : 바이트 단위 전송

- 보조 기억장치 : 블록(512바이트) 혹은 페이지(2K, 4K 바이트) 단위로 전송

- 제어기 내에 한 블록 이상을 임시 저장할 수 있는 데이터 기억장치(버퍼) 필요

컴퓨터 시스템의 전체 구성

2. 정보의 표현과 저장

컴퓨터 정보

- 2진수 비트들로 표현된 프로그램 코드와 데이터

프로그램 코드

- 기계어(machine language)

- 기계 코드(machine code)라고도 함

- 컴퓨터 하드웨어 부품들이 이해할 수 있는 언어로서, 2진 비트들로 구성

- 어셈블리 언어(assembly language)

- 고급 언어와 기계어 사이의 중간 언어

- 어셈블러(assembler)로 번역되며, 기계어와 일대일 대응

- 고급 언어(high-level language)

- 영문자와 숫자로 구성되어 사람이 이해하기 쉬운 언어

- C, C++, JAVA, Python 등

- 컴파일러(compiler)를 이용하여 기계어로 번역

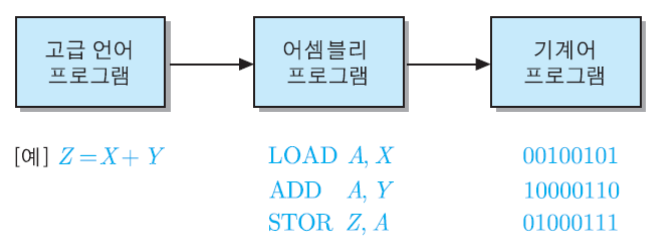

프로그램 언어의 번역 과정

프로그램은 고급언어 -> 어셈블리어 -> 기계어 순으로 변환

[예] Z = X + Y

- LOAD A, X : 기억장치 X 번지의 내용을 읽어서, 레지스터 A에 적재(load) 하라는 의미

- ADD A, Y : 기억장치 Y번지 내용을 읽어서, 레지스터 A에 적재된 값과 더하고, 결과를 다시 A에 적재하라는 의미

- STOR Z, A : 그 값을 기억장치 Z 번지에 저장 (store)

프로그램 언어 번역 소프트웨어

컴파일러(compiler)

- 고급언어 프로그램을 기계어 프로그램으로 번역하는 소프트웨어

어셈블러(assembler)

- 어셈블리 프로그램을 기계어 프로그램으로 번역하는 소프트웨어

- 니모닉스(mnemonics)

- 어셈블리 명령어가 지정하는 연산을 가리키는 알파벳 기호

- 'LOAD', 'ADD', 'STOR' 등

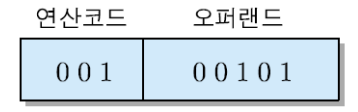

기계어(machine language)의 형식

연산코드(operation code, OP code)

- CPU가 수행할 연산을 지정해 주는 비트들

- 비트수 = '3'이라면, 지정될 수 있는 연산의 최대 수 : 23 = 8개

오퍼랜드(operand, 피연산자)

- 연산에 사용될 데이터 혹은 데이터가 저장되어 있는 기억장치 주소(memory address)

- 비스 수 = '5'라면, 주소지정(addressing) 할 수 있는 기억 장소의 최대 수 : 25 = 32 개

프로그램 코드와 데이터의 기억장치 저장

프로그램 코드(명령어)와 데이터는 지정된 기억 장소에 저장

단어(word) 단위로 저장

- 단어 : 각 기억장소에 저장되는 정보의 기본 단위로서, CPU에 의해 한번에 처리될 수 있는 비트들의 그룹

- 단어 길이의 예 : 8비트, 16비트, 32비트, 64비트

- 주소지정 단위 : 단어 단위 혹은 바이트(byte) 단위